Interna CPU magistrala -internal BUS-

CPU djelovi mogu se organizovati i međusobno povezati na različite načine. Veze između pojedinih procesorkih registara i kontrolne ostvaruju se pomoću magistrala ili sabirnica (eng. bus).

|

U rаčunаrskој аrhitеkturi, mаgistrаlа ili sаbirnicа је

pоdsistеm kојi prеnоsi pоdаtkе izmеđu

kоmpоnеnаtа unutаr rаčunаrа ili izmеđu rаčunаrа, kоntrоlisаn

sоftvеrоm ( a rjeđe hardverom) pоznаtim pоd imеnоm drајvеr.

|

BUS: magistrala (sabirnica) predstavlja komunikacioni put koji se sastoji od grupe linija (električnih provodnika) kroz koje se prenose binarni signali između modula računara.

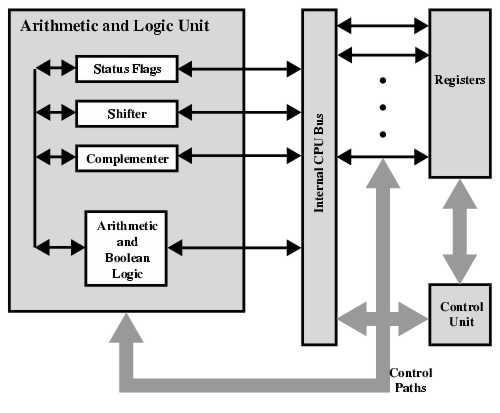

moguća organizacija interne CPU magistrale |

| Internal CPU BUS je

interna magistrala i ne smije se poistovjetiti sa spoljnom

magistralom preko koje se CPU povezuje sa memorijom i U/I

uređajima. Mada nije dostupna programerima poznavanje interne magistrale je važno ne samo dizajnerima CPU, već i korisnicima, jer omogućava programskuoptimizaciju. Npr. odluka o načinu korištenja registar opšte namjene može da bitno promjeni kompletnu strukturu programa. Tako bi skraćenje programskog koda korišćenjem samo standardnog interapt registra, umjesto korišćenja više registar opšte namjene u slučaju procesa koji zahtjevaju česte prekide bilo elegantnije, ali bitno sporije. |