Prenos podataka između CPU i ostatka računarskog sistema

Da bi se ostvarila komunikacija između pojedinih dijelova računara koriste se različite skupine veza: različite magistrale. Takođe je neophodno ostvariti vezu sa CPU modulima i njegovom internom magistralom. Povezivanje ovih magistrala obavlja se pomoću ulazno-izlaznih međusklopova (interfaces).

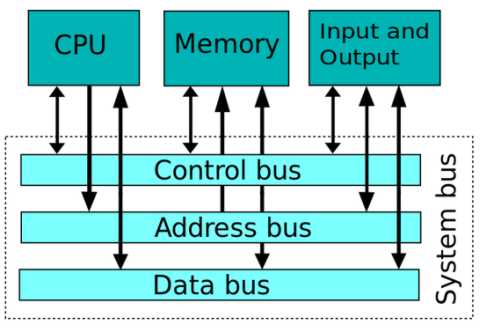

Postoje tri osnovna tipa magistrala joji zajedno čine sistemsku magistralu (eng. System bus):

1. Upravljačka magistrala -magistrala kontrole (eng. control bus) se sastoji iz linija kroz koje teku upravljački (komandni) signali. Većina upravljačkih signala potiče iz centralnog procesora. Ti signali određuju operaciju koja treba da se obavi i obezbeđuju sinhronizaciju između modula. Karakteristični signali su:

- sinhronizacioni signali,

- signali o stanju procesora,

- signali za dovođenje procesora u početno stanje, itd.

- signali zahtjeva za oslobađanje magistrale,

1. Magistrala adresa (eng.

address bus) prenosi signale koji se koriste za određivanje

adrese u primarnoj memoriji. Adresna magistrala se koristi za

označavanje izvora ili odredišta podataka. Ona omogućava da se svakoj

memorijskoj lokaciji, registru, I/O port-u, modulu itd. dodeli sopstvena

adresa. Signali na adresnim linijama obično dolaze od centralnog

procesora. Širina adresne magistrale (broj linija) određuje maksimalni

kapacitet memorijskog prostora. Najmanja širina od 16 BITA (linija)

omogućava adresiranje ukupno 216 = 65536 lokacija. Savremeni procesori

zahtjevaju sve veću operativnu memoriju (trenutno aktuelno 256, 512 MB

RAM-a). Zbog toga se mora proširivati i adresna magistrala (čak do 32

BITA).

3. Magistrala podataka (eng. data bus)

se koristi za prenos podataka ka operativnoj memoriji i između modula

sistema. Broj linija za podatke iznosi 8 (byte), 16 (word) ili 32

(double word).

Unutrašnja magistrala centralnog procesora je odvojena od spoljašnje magistrale podataka posredstvom kola sa tri stanja.

Upravljanje magistralom

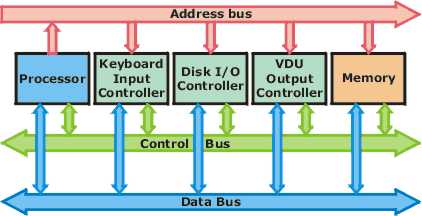

Iako je na magistralu povezano mnoštvo komponenti, u jednom trenutku vremena, u prenosu podataka učestvuju samo dvije. Ostali sklopovi ne učestvuju u prenosu, u datom trenutku, ali i ne smijeju ometati prenos između aktivnih komponenti.

Ovo je moguće ostvariti zahvaljujući primeni buffer registara i specijalne klase logičkih kola u izradi računarskih sklopova. To su logička kola sa tri stanja, tj. ova kola mogu biti u stanju logičke nule, jedinice i beskonačne impedanse. Kada su digitalna kola u stanju beskonačne impedanse, ona kao da nisu povezana na magistralu, tj. kao da ne postoje.

Prenos podataka duž magistrala dodatno komplikuje činjenica da svi dijelovi računarskog sistema koji su povezani na magistralu nemaju istu brzinu rada, pa treba izbjeći čekanje na odziv sporih uređaja..

Magistralom se upravlja pomoću posebnog funkcionalnog bloka koji se naziva kontroler magistrale. To može biti poseban modul ili dio centralnog procesora.

Upravljanje magistralom može biti centralizovano (prenosom podataka upravlja kontroler magistrale) ili decentralizovano (prenosom podataka upravlja modul koji je trenutno dobio magistralu na korišćenje).

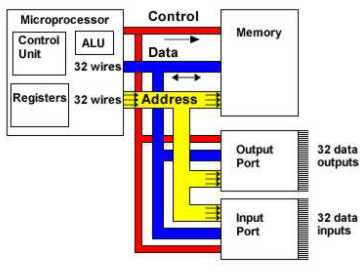

Kad se procesor želi da pošalje podatak

magistralom podataka, istovremeno se adresnom magistralom šalje adresa

komponente ili memorijske lokacije kojoj je podatak upućen, a kontrolnom

magistralom signal (komanda) za upis. Kada komponenta prepozna svoju

adresu na adresnoj magistrali, ona na osnovu komande koju čita sa

kontrolne magistrale zna da treba da preuzme podatak sa magistrale

podataka.

Kada procesor traži podatak od komponente ili memorijske

lokacije, on šalje adresu komponente adresnom magistralom, a

kontrolnom magistralom upucćje signal uređaju ili memoriji da se traženi

podatak pošalje magistralom podataka .

Tipični komandni signali koji se mogu naći na kontrolnoj magistrali su:

upis u memoriju, čitanje iz memorije, upis na U/I uređaj, čitanje sa U/I

uređaja, zahtev za magistralu, odobrenje magistrale, zahtev za prekidom,

reset.

Dakle, da bi modul primio podatke od drugog modula on mora:

- dobiti magistralu na korišćenje,

- poslati signal zahtjeva za prenos drugom modulu,

- čekati da drugi modul pošalje zahtjevane podatke, i

- primiti podatke preko magistrale.

Metode kontrole pristupa magistrali (vrste arbitraže)

Magistrali istovremeno pristupa više

uređaja istovremeno.

Metode kontrole pristupa se mogu klasifikovati kao:

- Centralizovane – postoji jedan hardverski element,

kontroler magistrale, koji je odgovoran za dodelu-oduzimanje pristupa

magistrali pojedinačnim uređajima.

- Distribuirane – svaki modul koji pristupa magistrali

sadrži komponentu upravljačke logike kojim se prenosni medijum

(magistrala) zauzima u određenom vremenskom periodu za prenos podataka.

Centralizovana arbitraža

Distribuirana arbitraža

Veličina koja pokazuje prenosnu moć magistrale je nivo transfera magistrale (T) i predstavlja proizvod učestanosti na kojoj radi magistrala (f) i širine magistrale podataka (D): T= f * D

Ako je učestanost na kojoj radi magistrala f=8 MHz, a širina magistrale podataka D=16b,

nivo transfera je T=128 Mb/s.

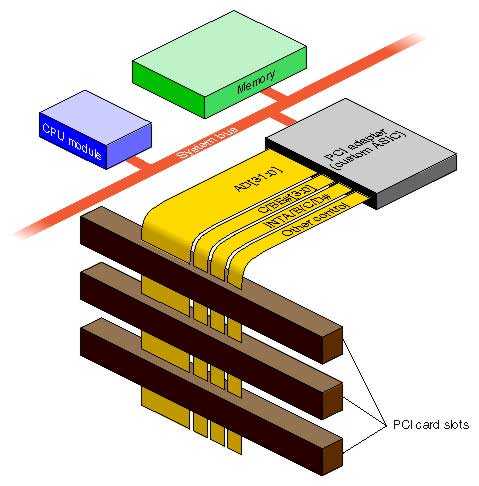

Predstava sistemske sabirnice kod PC računara

Istorija i razvoj magistrala:

Prvа gеnеrаciја

Kоd stаriјih rаčunаrа mаgistrаlе su bilе gоmilа žicа pоvеzаnih sа

mеmоriјоm i pеrifеrnim urеđајimа. Skоrо uvijеk је pоstојаlа јеdnа

mаgistrаlа zа mеmоriјu i јеdnа zа pеrifеrnе urеđаје i njimа sе

pristupаlо pоmоću pоsеbnih instrukciја, drugаčiјеg tајmingа i prоtоkоlа.

Kоmplikаciја оvаkvе rеаlizаciје је bilа оbrаdа prеkidа (interapta). Dа

bi sе izvršilа ulаznо-izlаznа оpеrаciја prоgrаm је mоrао čеkаti dа

pеrifеriја pоstаnе sprеmnа.

Drugа gеnеrаciја

Drugа gеnеrаciја mаgistrаlа, kао Nu mаgistrаlа (NuBus), rjеšаvа nеkе оd

оvih prоblеmа. Оnа је pоdijеlilа rаčunаr nа dvа „svijet“,

prоcеsоr i mеmоriјu nа јеdnu strаnu i rаznе urеđаје nа

drugu, sа kоntrоlеrоm izmеđu njih. Оvо је

оmоgućilо dа prоcеsоr pоvеćа brzinu bеz uticаја nа mаgistrаlu.

Trеćа gеnеrаciја

Тrеćа gеnеrаciја mаgistrаlа tеk dоlаzi i uklјučuје

HyperTransport i InfiniBand

mаgistrаlе. Оnе sаdržе оsоbinе kоје im оmоgućuјu dа rаdе nа vrlо visоkim

brzinаmа kаkо bi pоdržаlе mеmоriјu i grаfičkе kаrticе, аli tаkоđе

pоdržаvајu spоriје brzinе zа kоmunikаciјu sа spоrim urеđајimа kао štо su

diskоvi.